HBM steht für High Bandwidth Memory und ist eine Art von Speicherschnittstelle, die in 3D-gestapeltem DRAM (Dynamic Random Access Memory) in einigen AMD-GPUs (auch bekannt als Grafikkarten) sowie in Servern, High Performance Computing (HPC) und Netzwerken verwendet wird und Kundenbereich. Samsung und SK Hynix stellen HBM-Chips her.

Letztendlich soll HBM im Vergleich zum GDDR-Speicher, der in den meisten der besten heutigen Grafikkarten für Spiele verwendet wird, eine viel höhere Bandbreite und einen geringeren Stromverbrauch bieten.

HBM-Spezifikationen

HBM2 / HBM2E (Aktuell)

HBM

HBM3 (demnächst)

Max. PIN-Übertragungsrate

3,2 Gbit/s

1 Gbit/s

?

Maximale Kapazität

24 GB

4GB

64 GB

Maximale Bandbreite

410 GBps

128 GB/s

512 GBps

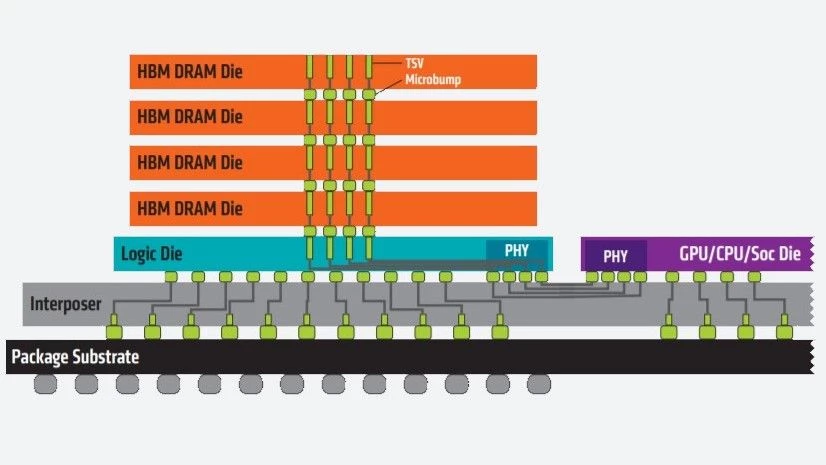

Die HBM-Technologie funktioniert durch vertikales Stapeln von Speicherchips übereinander, um die Datenübertragungsstrecke zu verkürzen und gleichzeitig kleinere Formfaktoren zu ermöglichen. Darüber hinaus ist der Speicherbus von HBM mit zwei 128-Bit-Kanälen pro Die viel breiter als der anderer DRAM-Speichertypen.

Gestapelte Speicherchips werden über Through-Silicon Vias (TSVs) und Microbumps verbunden und über den Interposer mit der GPU verbunden, anstatt auf dem Chip.

HBM2 und HBM2E

HBM2 wurde 2016 eingeführt und im Dezember 2018 aktualisierte die JEDEC den HBM2-Standard. Der aktualisierte Standard wurde allgemein sowohl als HBM2 als auch als HBM2E bezeichnet (um die Abweichung vom ursprünglichen HBM2-Standard zu bezeichnen). Die Spezifikation wurde jedoch Anfang 2020 erneut aktualisiert, und der Name „HBM2E“ wurde nicht offiziell aufgenommen. Dank Micron kann es jedoch vorkommen, dass Personen und/oder Unternehmen HBM2 als HBM2E oder sogar HBMnext bezeichnen.

Der aktuelle HBM2-Standard ermöglicht eine Bandbreite von 3,2 GBps pro Pin mit einer maximalen Kapazität von 24 GB pro Stack (2 GB pro Die über 12 Dies pro Stack) und einer maximalen Bandbreite von 410 GBps, die über eine 1.024-Bit-Speicherschnittstelle geliefert wird, die durch 8 eindeutige getrennt ist Kanäle auf jedem Stack.

Ursprünglich wurde HBM2 für eine maximale Übertragungsrate von 2 GBps pro Pin, eine maximale Kapazität von 8 GB pro Stack (1 GB maximale Die-Kapazität über 8 Dies pro Stack) und eine maximale Bandbreite von 256 GBps spezifiziert. Es wurde dann auf 2,4 Gbps pro Pin und eine maximale Kapazität von 24 GB (2 GB pro Die über 12 Dies pro Stack) und eine maximale Bandbreite von 307 Gbps erhöht, bevor es den heutigen Standard erreichte.

HBM3

Obwohl noch nicht verfügbar, wird der HBM3-Standard derzeit diskutiert und von JEDEC standardisiert.

Laut einem Bericht von Ars Technica soll HBM3 Kapazitäten von bis zu 64 GB und eine Bandbreite von bis zu 512 GBps unterstützen. Im Jahr 2019 wies Jeongdong Choe, Analyst bei TechInsights, in einem Interview mit Semiconductor Engineering darauf hin, dass HBM3 Übertragungsraten von 4 Gbps unterstützt. HBM3 wird Berichten zufolge auch mehr Chips pro Stack und mehr als die doppelte Dichte pro Chip mit einem ähnlichen Leistungsbudget liefern. In einem Blogbeitrag aus dem Jahr 2020 berichtete Cadence, dass die Spezifikation einen 512-Bit-Bus mit höheren Taktraten verwenden wird, wodurch HBM3 „die gleiche höhere Bandbreite mit viel geringeren Kosten erreichen kann, da kein Silizium-Interposer erforderlich ist“.

Wir kennen das Veröffentlichungsdatum von HBM3 noch nicht; Im April dieses Jahres sahen wir jedoch, wie SiFive ein System-on-Chip (SoC) mit HBM3 herausbrachte.

Dieser Artikel ist Teil des Tom’s Hardware-Glossar.

Weiterlesen:

Beste Grafikkarten

GPU-Benchmarks und Hierarchie