HBM è l’acronimo di memoria a larghezza di banda elevata ed è un tipo di interfaccia di memoria utilizzata nella DRAM 3D-stacked (memoria dinamica ad accesso casuale) in alcune GPU AMD (dette anche schede grafiche), nonché nel server, nel calcolo ad alte prestazioni (HPC) e nel networking e spazio per i clienti. Samsung e SK Hynix producono chip HBM.

In definitiva, la HBM ha lo scopo di offrire una larghezza di banda molto più elevata, un consumo energetico inferiore rispetto alla memoria GDDR utilizzata nella maggior parte delle migliori schede grafiche per i giochi di oggi.

Specifiche HBM

HBM2 / HBM2E (corrente)

HBM

HBM3 (prossimamente)

Velocità di trasferimento pin massima

3,2 Gbps

1 Gbps

?

Capacità massima

24 GB

4GB

64 GB

Larghezza di banda massima

410 Gbps

128 Gbps

512 Gbps

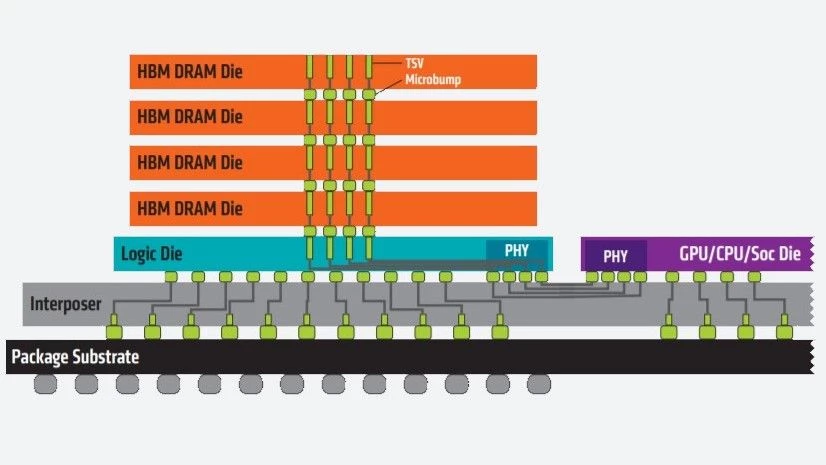

La tecnologia HBM funziona impilando verticalmente i chip di memoria uno sopra l’altro per ridurre la distanza percorsa dai dati, consentendo al contempo fattori di forma più piccoli. Inoltre, con due canali a 128 bit per die, il bus di memoria della HBM è molto più ampio di quello di altri tipi di memoria DRAM.

I chip di memoria impilati sono collegati tramite TSV (through-silicon vias) e microbump e si connettono alla GPU tramite l’interposer, anziché su chip.

HBM2 e HBM2E

HBM2 ha debuttato nel 2016 e nel dicembre 2018 JEDEC ha aggiornato lo standard HBM2. Lo standard aggiornato era comunemente indicato sia come HBM2 che come HBM2E (per indicare la deviazione dallo standard HBM2 originale). Tuttavia, le specifiche sono state nuovamente aggiornate all’inizio del 2020 e il nome “HBM2E” non è stato formalmente incluso. Tuttavia, potresti ancora vedere persone e/o aziende fare riferimento a HBM2 come HBM2E o addirittura HBMnext, grazie a Micron.

L’attuale standard HBM2 consente una larghezza di banda di 3,2 GBps per pin con una capacità massima di 24 GB per stack (2 GB per die su 12 die per stack) e una larghezza di banda massima di 410 GBps, fornita su un’interfaccia di memoria a 1.024 bit separata da 8 univoci canali su ogni stack.

Originariamente, HBM2 prevedeva una velocità di trasferimento massima di 2 GBps per pin, una capacità massima di 8 GB per stack (capacità massima di 1 GB su 8 die per stack) e una larghezza di banda massima di 256 GBps. È stato quindi aumentato a 2,4 Gbps per pin e una capacità massima di 24 GB (2 GB per die su 12 die per stack) e una larghezza di banda massima di 307 Gbps prima di raggiungere lo standard che vediamo oggi.

HBM3

Sebbene non sia ancora disponibile, lo standard HBM3 è attualmente in discussione e standardizzato da JEDEC.

Secondo un rapporto di Ars Technica, HBM3 dovrebbe supportare capacità fino a 64 GB e una larghezza di banda fino a 512 GBps. Nel 2019, Jeongdong Choe, analista di TechInsights, ha indicato che HBM3 supporta velocità di trasferimento di 4 Gbps in un’intervista con Semiconductor Engineering. Secondo quanto riferito, HBM3 fornirà anche più stampi per pila e più del doppio della densità per die con un budget di potenza simile. In un post sul blog del 2020, Cadence ha riferito che le specifiche utilizzeranno un bus a 512 bit con clock più elevati, consentendo a HBM3 di “ottenere la stessa larghezza di banda più elevata con costi molto inferiori non richiedendo un interposer di silicio”.

Non conosciamo ancora la data di rilascio di HBM3; tuttavia, questo aprile abbiamo visto SiFive registrare un system-on-chip (SoC) con HBM3.

Questo articolo fa parte del Glossario hardware di Tom.

Ulteriori letture:

Le migliori schede grafiche

Benchmark e gerarchia della GPU