HBM significa memoria de alto ancho de banda y es un tipo de interfaz de memoria utilizada en DRAM apilada en 3D (memoria dinámica de acceso aleatorio) en algunas GPU AMD (también conocidas como tarjetas gráficas), así como en el servidor, la computación de alto rendimiento (HPC) y las redes. y espacio para el cliente. Samsung y SK Hynix fabrican chips HBM.

En última instancia, HBM está destinado a ofrecer un ancho de banda mucho mayor y un menor consumo de energía en comparación con la memoria GDDR utilizada en la mayoría de las mejores tarjetas gráficas para juegos de la actualidad.

Especificaciones de HBM

HBM2 / HBM2E (Actual)

HBM

HBM3 (próximamente)

Tasa máxima de transferencia de PIN

3,2 Gb/s

1 Gbps

?

Máxima capacidad

24GB

4 GB

64GB

El ancho de banda máximo

410 GB/s

128 GB/s

512 GB/s

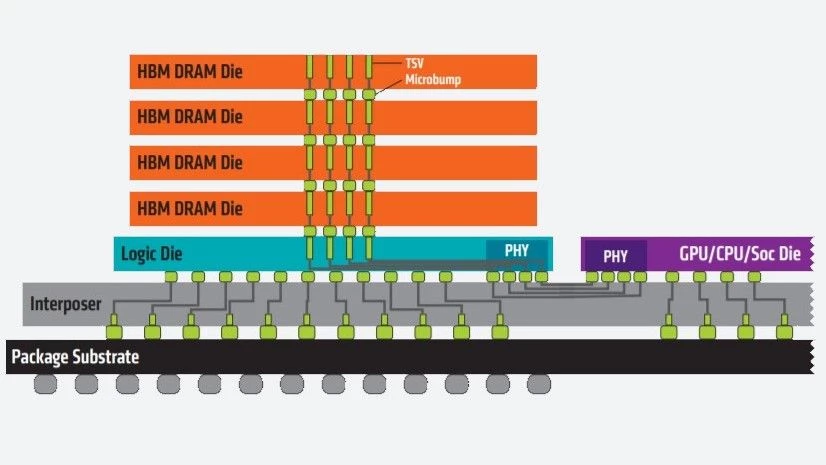

La tecnología de HBM funciona mediante el apilamiento vertical de chips de memoria uno encima del otro para acortar la distancia que deben viajar los datos, al tiempo que permite factores de forma más pequeños. Además, con dos canales de 128 bits por matriz, el bus de memoria de HBM es mucho más amplio que el de otros tipos de memoria DRAM.

Los chips de memoria apilados se conectan a través de vías de silicio (TSV) y microbaches y se conectan a la GPU a través del intercalador, en lugar de en el chip.

HBM2 y HBM2E

HBM2 debutó en 2016 y, en diciembre de 2018, JEDEC actualizó el estándar HBM2. El estándar actualizado se denominaba comúnmente HBM2 y HBM2E (para indicar la desviación del estándar HBM2 original). Sin embargo, la especificación se actualizó nuevamente a principios de 2020 y el nombre «HBM2E» no se incluyó formalmente. Sin embargo, es posible que aún vea personas y/o empresas que se refieren a HBM2 como HBM2E o incluso HBMnext, gracias a Micron.

El estándar HBM2 actual permite un ancho de banda de 3,2 GBps por pin con una capacidad máxima de 24 GB por pila (2 GB por troquel en 12 troqueles por pila) y un ancho de banda máximo de 410 GBps, entregado a través de una interfaz de memoria de 1024 bits separada por 8 únicos canales en cada pila.

Originalmente, HBM2 se especificó para una tasa de transferencia máxima de 2 GBps por pin, una capacidad máxima de 8 GB por pila (capacidad máxima de matriz de 1 GB en 8 matrices por pila) y un ancho de banda máximo de 256 GBps. Luego se elevó a 2,4 Gbps por pin y una capacidad máxima de 24 GB (2 GB por matriz en 12 matrices por pila) y un ancho de banda máximo de 307 Gbps antes de alcanzar el estándar que vemos hoy.

HBM3

Si bien aún no está disponible, el estándar HBM3 se encuentra actualmente en discusión y está siendo estandarizado por JEDEC.

Según un informe de Ars Technica, se espera que HBM3 admita capacidades de hasta 64 GB y un ancho de banda de hasta 512 GBps. En 2019, Jeongdong Choe, analista de TechInsights, señaló que HBM3 admitía tasas de transferencia de 4 Gbps en una entrevista con Semiconductor Engineering. Según se informa, HBM3 también entregará más troqueles por pila y más del doble de densidad por troquel con un presupuesto de energía similar. En una publicación de blog de 2020, Cadence informó que la especificación usará un bus de 512 bits con relojes más altos, lo que permitirá que HBM3 «logre el mismo ancho de banda más alto con un costo mucho menor al no requerir un intercalador de silicio».

Aún no sabemos la fecha de lanzamiento de HBM3; sin embargo, este abril vimos a SiFive grabar un sistema en chip (SoC) con HBM3.

Este artículo es parte del Glosario de hardware de Tom.

Otras lecturas:

Las mejores tarjetas gráficas

Puntos de referencia y jerarquía de GPU