HBM là viết tắt của bộ nhớ băng thông cao và là một loại giao diện bộ nhớ được sử dụng trong DRAM xếp chồng 3D (bộ nhớ truy cập ngẫu nhiên động) trong một số GPU AMD (hay còn gọi là cạc đồ họa), cũng như máy chủ, máy tính hiệu năng cao (HPC) và mạng và không gian khách hàng. Samsung và SK Hynix sản xuất chip HBM.

Cuối cùng, HBM có nghĩa là cung cấp băng thông cao hơn nhiều, tiêu thụ điện năng thấp hơn so với bộ nhớ GDDR được sử dụng trong hầu hết các card đồ họa tốt nhất hiện nay để chơi game.

Thông số kỹ thuật HBM

HBM2 / HBM2E (Hiện tại)

HBM

HBM3 (Sắp ra mắt)

Tốc độ truyền pin tối đa

3,2 Gb / giây

1 Gb / giây

?

Công suất tối đa

24GB

4GB

64GB

Băng thông tối đa

410 GBps

128 GBps

512 GBps

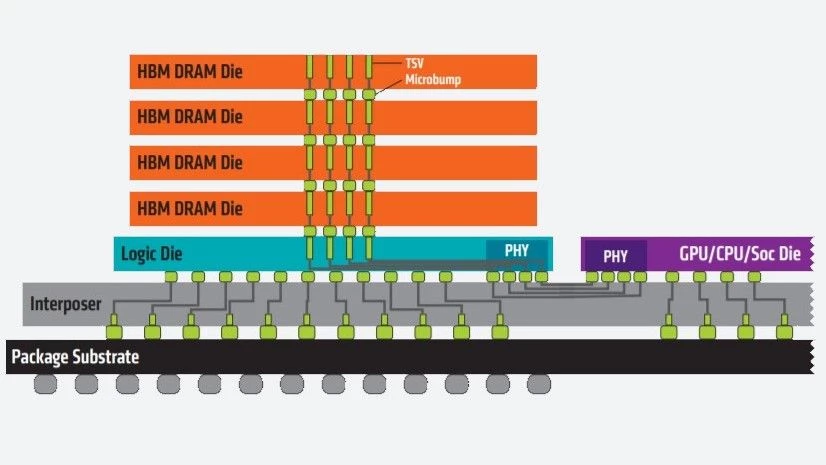

Công nghệ HBM hoạt động bằng cách xếp chồng các chip nhớ theo chiều dọc lên nhau để rút ngắn khoảng cách dữ liệu phải di chuyển, đồng thời cho phép các hệ số dạng nhỏ hơn. Ngoài ra, với hai kênh 128 bit trên mỗi khuôn, bus bộ nhớ của HBM rộng hơn nhiều so với các loại bộ nhớ DRAM khác.

Các chip nhớ xếp chồng được kết nối thông qua vias silicon (TSV) và microbumps và kết nối với GPU thông qua interposer, chứ không phải trên chip.

HBM2 và HBM2E

HBM2 ra mắt vào năm 2016 và vào tháng 12 năm 2018, JEDEC đã cập nhật tiêu chuẩn HBM2. Tiêu chuẩn cập nhật thường được gọi là cả HBM2 và HBM2E (để biểu thị độ lệch so với tiêu chuẩn HBM2 ban đầu). Tuy nhiên, thông số kỹ thuật đã được cập nhật lại vào đầu năm 2020 và tên “HBM2E” không được chính thức đưa vào. Tuy nhiên, bạn vẫn có thể thấy mọi người và / hoặc các công ty gọi HBM2 là HBM2E hoặc thậm chí là HBMnext, nhờ Micron.

Tiêu chuẩn HBM2 hiện tại cho phép băng thông 3,2 GBps trên mỗi chân với dung lượng tối đa 24 GB trên mỗi ngăn xếp (2GB trên mỗi ô trên 12 ô trên mỗi ngăn xếp) và băng thông tối đa là 410 GBps, được phân phối trên giao diện bộ nhớ 1.024 bit, cách nhau 8 điểm. các kênh trên mỗi ngăn xếp.

Ban đầu, HBM2 được chỉ định cho tốc độ truyền tối đa là 2 GBps mỗi chân, dung lượng tối đa 8GB mỗi ngăn xếp (dung lượng khuôn tối đa 1GB trên 8 khuôn trên mỗi ngăn xếp) và băng thông tối đa 256 GBps. Sau đó, nó đã được tăng lên 2,4 Gbps trên mỗi chân và dung lượng tối đa là 24GB (2GB mỗi khuôn trên 12 khuôn trên mỗi ngăn xếp) và băng thông tối đa 307 Gbps trước khi đạt đến tiêu chuẩn mà chúng ta thấy ngày nay.

HBM3

Mặc dù chưa có sẵn nhưng tiêu chuẩn HBM3 hiện đang được thảo luận và đang được chuẩn hóa bởi JEDEC.

Theo báo cáo của Ars Technica, HBM3 dự kiến sẽ hỗ trợ dung lượng lên đến 64GB và băng thông lên đến 512 GBps. Vào năm 2019, Jeongdong Choe, một nhà phân tích tại TechInsights, đã chỉ ra rằng HBM3 hỗ trợ tốc độ truyền 4 Gbps trong một cuộc phỏng vấn với Semiconductor Engineering. Theo báo cáo, HBM3 cũng sẽ cung cấp nhiều khuôn trên mỗi ngăn xếp và hơn hai lần mật độ trên mỗi khuôn với một ngân sách năng lượng tương tự. Trong một bài đăng trên blog năm 2020, Cadence đã báo cáo rằng thông số kỹ thuật sẽ sử dụng một bus 512 bit với xung nhịp cao hơn, cho phép HBM3 “đạt được cùng một băng thông cao hơn với chi phí thấp hơn nhiều bằng cách không yêu cầu bộ xen kẽ silicon”.

Chúng tôi chưa biết ngày phát hành của HBM3; tuy nhiên, vào tháng 4 này, chúng ta đã thấy SiFive tung ra hệ thống trên chip (SoC) với HBM3.

Bài viết này là một phần của Tom’s Hardware Glossary.

Đọc thêm:

Cạc đồ họa tốt nhất

Điểm chuẩn và phân cấp GPU