HBM significa memória de alta largura de banda e é um tipo de interface de memória usada em 3D-stacked DRAM (memória dinâmica de acesso aleatório) em algumas GPUs AMD (também conhecidas como placas gráficas), bem como no servidor, computação de alto desempenho (HPC) e rede e espaço do cliente. Samsung e SK Hynix fabricam chips HBM.

Em última análise, a HBM deve oferecer largura de banda muito maior, menor consumo de energia em comparação com a memória GDDR usada na maioria das melhores placas gráficas atuais para jogos.

Especificações HBM

HBM2 / HBM2E (Atual)

HBM

HBM3 (Próximo)

Taxa máxima de transferência de pinos

3,2 Gbps

1 Gbps

?

Capacidade máxima

24 GB

4GB

64 GB

Largura de banda máxima

410 GBps

128 GBps

512 GBps

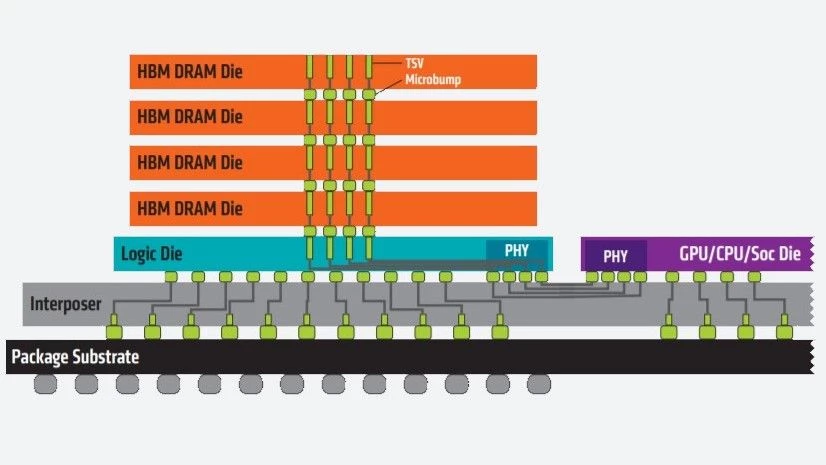

A tecnologia HBM funciona empilhando verticalmente os chips de memória uns sobre os outros para reduzir a distância que os dados precisam percorrer, enquanto permite formatos menores. Além disso, com dois canais de 128 bits por matriz, o barramento de memória da HBM é muito mais amplo que o de outros tipos de memória DRAM.

Os chips de memória empilhados são conectados através de vias de silício (TSVs) e microbumps e se conectam à GPU por meio do interposer, em vez de no chip.

HBM2 e HBM2E

O HBM2 estreou em 2016 e, em dezembro de 2018, o JEDEC atualizou o padrão HBM2. O padrão atualizado era comumente referido como HBM2 e HBM2E (para denotar o desvio do padrão HBM2 original). No entanto, a especificação foi atualizada novamente no início de 2020 e o nome “HBM2E” não foi formalmente incluído. No entanto, você ainda pode ver pessoas e/ou empresas se referirem ao HBM2 como HBM2E ou mesmo HBMnext, graças à Micron.

O padrão HBM2 atual permite uma largura de banda de 3,2 GBps por pino com capacidade máxima de 24 GB por pilha (2 GB por matriz em 12 matrizes por pilha) e largura de banda máxima de 410 GBps, fornecida em uma interface de memória de 1.024 bits separada por 8 canais em cada pilha.

Originalmente, o HBM2 foi especificado para uma taxa de transferência máxima de 2 GBps por pino, uma capacidade máxima de 8 GB por pilha (capacidade máxima de matriz de 1 GB em 8 matrizes por pilha) e largura de banda máxima de 256 GBps. Ele foi então aumentado para 2,4 Gbps por pino e uma capacidade máxima de 24 GB (2 GB por matriz em 12 matrizes por pilha) e uma largura de banda máxima de 307 Gbps antes de atingir o padrão que vemos hoje.

HBM3

Embora ainda não esteja disponível, o padrão HBM3 está atualmente em discussão e sendo padronizado pelo JEDEC.

De acordo com um relatório da Ars Technica, espera-se que o HBM3 suporte capacidades de até 64 GB e uma largura de banda de até 512 GBps. Em 2019, Jeongdong Choe, analista da TechInsights, apontou que o HBM3 suporta taxas de transferência de 4 Gbps em uma entrevista à Semiconductor Engineering. O HBM3 também fornecerá mais matrizes por pilha e mais de duas vezes a densidade por matriz com um orçamento de energia semelhante. Em uma postagem no blog de 2020, a Cadence informou que a especificação usará um barramento de 512 bits com clocks mais altos, permitindo que o HBM3 “obtenha a mesma largura de banda mais alta com custo muito menor, não exigindo um interposer de silício”.

Ainda não sabemos a data de lançamento do HBM3; no entanto, em abril deste ano vimos SiFive gravar um system-on-chip (SoC) com HBM3.

Este artigo faz parte do Glossário de Hardware do Tom.

Leitura adicional:

Melhores placas gráficas

Benchmarks e hierarquia de GPU